#### Unit-1

### UNIT – I 8 BIT EMBEDDED PROCESSOR

Microcontrollers for an Embedded System – 8051 – Architecture – Addressing Modes – Instruction Set – Program and Data Memory – Stacks – Interrupts – Timers/Counters – Serial Ports – Programming.

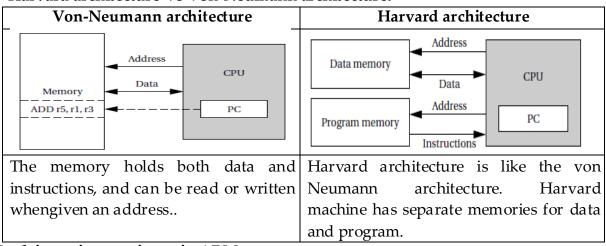

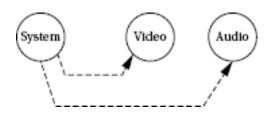

### Microcontrollers for Embedded system:

- $\checkmark$  A Microcontroller is a single chip computer.

- ✓ A CPU with all the peripherals like RAM, ROM, I/O Ports, Timers, and ADCs etc. on the same chip. For Ex: Motorola 6811, Intel 8051, Zilog Z8 and PIC 16X etc...

### Microprocessor:

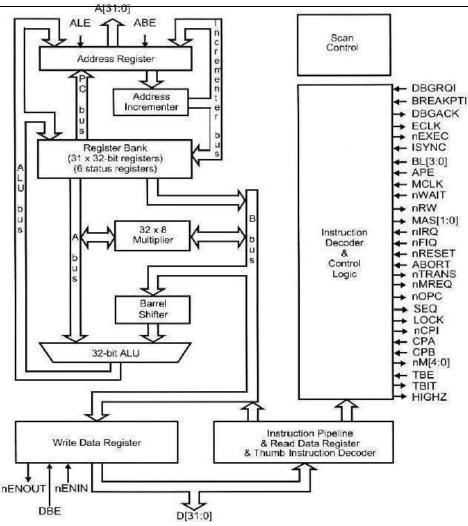

- $\checkmark$  A CPU built into a single VLSI chip is called a microprocessor.

- ✓ It is a general-purpose device and additional external circuitry is added to make it a microcomputer.

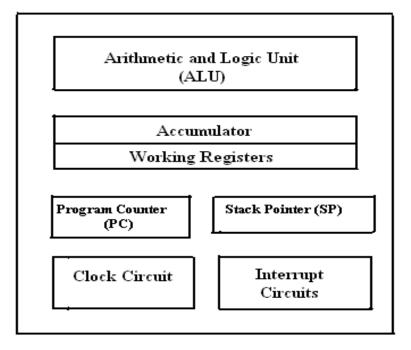

- ✓ The microprocessor contains arithmetic logic unit (ALU), Control unit, Instruction register, Program counter (PC), clock circuit (internal or external), reset circuit (internal or external) and registers.

- ✓ But the microprocessor has no on chip I/O Ports, Timers, Memory etc.

- ✓ For example, Intel 8085 is an 8-bit microprocessor and Intel 8086/8088 a 16-bit microprocessor.

- ✓ The block diagram of the Microprocessor is shown in Fig.1

Fig.1: Block diagram of a Microprocessor.

Unit-1

# MICROCONTROLLER :

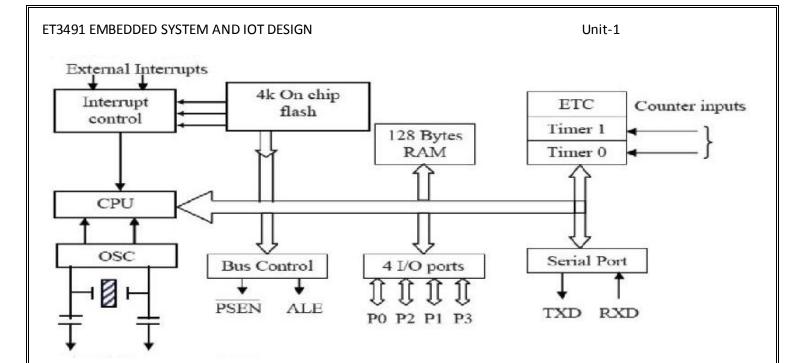

- ✓ A microcontroller is an integrated single chip, which consists of CPU, RAM, EPROM/PROM/ROM, I/O ports, timers, interrupt controller.

- ✓ For example, Intel 8051 is 8-bit microcontroller and Intel 8096 is 16-bit microcontroller.

- ✓ The block diagram of Microcontroller is shown in Fig.2.

| Microcontro | ller |       |                       |

|-------------|------|-------|-----------------------|

|             | СРU  | RAM   | ROM                   |

|             | I/O  | Timer | Serial<br>COM<br>Port |

### Fig.2.Block Diagram of a Microcontroller

### Distinguish between Microprocessor and Microcontroller

| S.No | Microprocessor                                                                      | Microcontroller                                                                                                         |

|------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 1    | A microprocessor is a general purpose device.                                       | A microcontroller is a dedicated chip which<br>is also called as single chip computer.                                  |

| 2    | A microprocessor does not contain<br>on chip I/O Ports, Timers,<br>Memories etc.    | A microcontroller includes RAM, ROM,<br>serial and parallel interface, timers,<br>interrupt circuitry in a single chip. |

| 3    | Microprocessor is used as the CPU in microcomputer system.                          | Microcontroller is used to perform control-<br>oriented applications.                                                   |

| 4    | Microprocessor instructions are<br>nibble or byte addressable                       | Microcontroller instructions are both bit<br>addressable as well as byte addressable.                                   |

| 5    | Microprocessor based system<br>design is complex and expensive                      | Microcontroller based system design is simple and cost effective                                                        |

| 6    | The Instruction set of microprocessor is complex with large number of instructions. | The instruction sets are simple with less number of instructions.                                                       |

### 4.2: INTEL 8051 MICRCONTROLLER:

Draw the architectural block diagram of 8051 microcontroller and explain. (NOV 2011, MAY 2010, NOV 2009, NOV2008, May 2008, MAY 2007, MAY 2006, NOV 2016, May 2016)

### Features of 8051 Microcontroller:

The 8051 is an 8-bit Controller:

- ✓ The CPU can works on only 8 bits of data at a time

- ✓ The 8051 has

- 128 bytes of RAM

- 4K bytes of on-chip ROM

- Two timers

- One serial port

- Four I/O ports, each 8 bits wide

- 6 interrupt sources

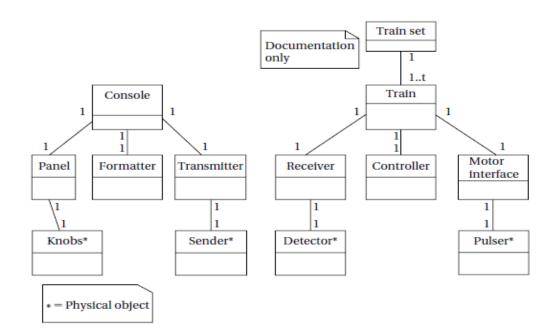

# ARCHITECTURE & BLOCK DIAGRAM OF 8051 MICROCONTROLLER:

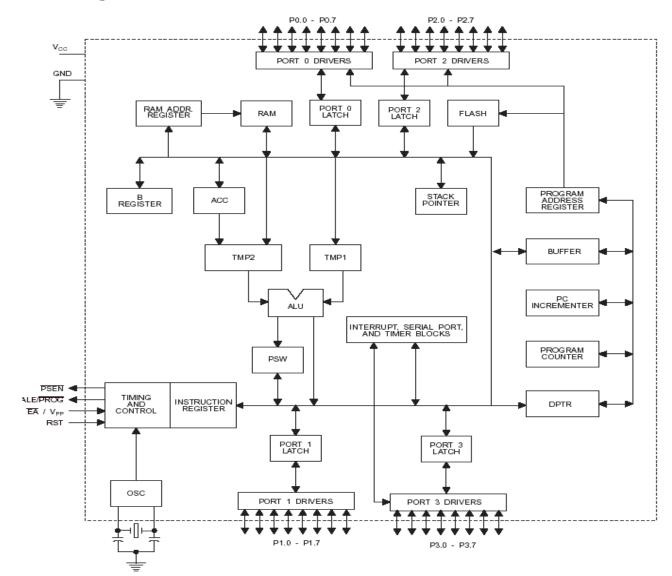

- ✓ It has hardware architecture with RISC (Reduced Instruction Set Computer) concept.

- $\checkmark$  The block diagram of 8051 microcontroller is shown in Fig 3.

- ✓ 8051 has 8-bit ALU.

- ✓ ALU can perform all the 8-bit arithmetic and logical operations in one machine cycle.

- $\checkmark$  The ALU is associated with two registers A & B

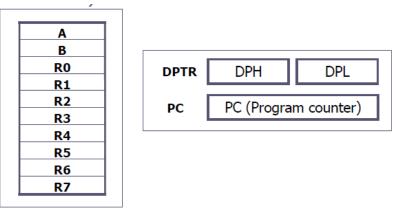

# A and B Registers:

- $\checkmark$  The A and B registers are special function registers.

- $\checkmark$  A & B registers hold the results of many arithmetic and logical operations of 8051.

- $\checkmark$  The A register is also called the **Accumulator.**

- $\checkmark$  A register is used as a general register to accumulate the results of a large number of instructions.

- ✓ By default, it is used for all mathematical operations and data transfer operations between CPU and external memory.

- ✓ The B register is mainly used for multiplication and division operations along with A register.

- Ex: MULAB : DIVAB.

- $\checkmark$  It has no other function other than as a store data.

### R registers:

- $\checkmark$  "R" registers are a set of eight registers that are named R0, R1, etc. up to R7.

- $\checkmark$  These registers are used as auxiliary registers in many operations.

- $\checkmark$  The "R" registers are also used to temporarily store values.

### Fig.3. Block Diagram of 8051 Microcontroller

### **Program Counter (PC) :**

- ✓ 8051 has a 16-bit program counter.

- $\checkmark$  The program counter holds address of the next instruction to be executed.

- $\checkmark$  After execution of one instruction, the program counter is incremented.

### Data Pointer Register (DPTR):

- $\checkmark$  It is a 16-bit register which is the only user-accessible.

- ✓ DPTR is used to point the data. 8051 will access external memory at the address indicated by DPTR.

- $\checkmark$  DPTR can also be used as two 8-registers DPH and DPL.

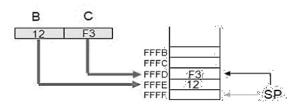

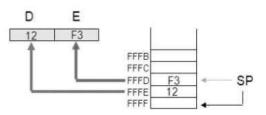

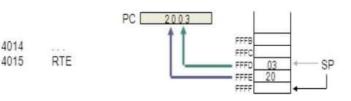

### Stack Pointer Register (SP) :

- $\checkmark$  It is an 8-bit register which stores the address of the stack top.

- ✓ When a value is pushed onto the stack, the 8051 first increments the value of SP and then stores the value.

- ✓ Similarly when a value is popped off the stack, the 8051 returns the value from the memory location indicated by SP and then decrements the value of SP.

- $\checkmark$  Since the SP is only 8-bit wide.

- $\checkmark$  It is incremented or decremented by two.

- ✓ SP is modified directly by the 8051 by six instructions: PUSH, POP, ACALL, LCALL, RET, and RETI.

- $\checkmark$  It is also used intrinsically whenever an interrupt is triggered.

#### Block Diagram

Fig: Structure of registers

• • • 5

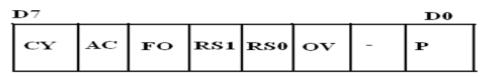

### Program Status Register (PSW):

### Give PSW of 8051 and describe the use of each bit in PSW. (NOV 2015)

- ✓ The 8051 has an 8-bit PSW register which is also known as Flag register.

- $\checkmark$  In the 8-bit register only 6-bits are used by 8051. The two unused bits are user definable bits.

- ✓ In the 6-bits, four of them are conditional flags. They are Carry –CY, Auxiliary Carry-AC, Parity-P, and Overflow-OV.

- $\checkmark$  These flag bits indicate some conditions of result after an instruction was executed.

- ✓ The bits PSW3 and PSW4 are denoted as RS0 and RS1.

- $\checkmark$  These bits are used to select the bank registers of the RAM location.

- $\checkmark$  The meaning of various bits of PSW register is shown below.

| CY  | PSW.7 | Carry Flag                            |

|-----|-------|---------------------------------------|

| AC  | PSW.6 | Auxiliary Carry Flag                  |

| FO  | PSW.5 | Flag 0 available for general purpose  |

| RS1 | PSW.4 | Register Bank select bit 1            |

| RS0 | PSW.3 | Register bank select bit 0            |

| OV  | PSW.2 | Overflow flag                         |

|     | PSW.1 | User definable flag                   |

| Р   | PSW.0 | Parity flag .set/cleared by hardware. |

$\checkmark$  The selection of the register Banks and their addresses are given below.

| RS1 | RS0 | Register Bank | Address |

|-----|-----|---------------|---------|

| 0   | 0   | 0             | 00H-07H |

| 0   | 1   | 1             | 08H-0FH |

| 1   | 0   | 2             | 10H-17H |

| 1   | 1   | 3             | 18H-1FH |

### RAM & ROM:

- ✓ The 8051 microcontroller has 128 bytes of Internal RAM and 4KB of on chip ROM.

- $\checkmark$  The RAM is also known as Data memory and the ROM is known as program (Code) memory.

- $\checkmark$  Code memory holds program that is to be executed.

- ✓ Program Address Register holds address of the ROM/ Flash memory.

- ✓ Data Address Register holds address of the RAM.

### I/O ports:

- ✓ The 8051 microcontroller has 4 parallel I/O ports, each of 8-bits.

- $\checkmark$  So, it provides 32 I/O lines for connecting the microcontroller to the peripherals.

- ✓ The four ports are P0 (Port 0), P1 (Port1), P2 (Port 2) and P3 (Port3).

### ADDRESSING MODES OF 8051 :

### Explain different types addressing modes of 8051 microcontroller. (NOV 2008, NOV 2015, April 2017)

- ✓ The way in which the data operands are specified is known as the addressing modes. There are various methods of denoting the data operands in the instruction.

- ✓ The 8051 microcontroller supports 5 addressing modes. They are

- 1. Immediate addressing mode

- 2. Direct Addressing mode

- 3. Register addressing mode

- 4. Register indirect addressing mode

- 5. Indexed addressing mode

### Immediate addressing mode:

- ✓ The addressing mode in which the data operand is a constant and it is a part of the instruction itself is known as Immediate addressing mode.

- $\checkmark$  Normally the data must be preceded by a # sign.

$\checkmark$  This addressing mode can be used to transfer the data into any of the registers including DPTR. Examples:

- MOV A, # 27 H : The data (constant) 27 is moved to the accumulator register

- ADD R1, #45 H : Add the constant 45 to the contents of the accumulator

- MOV DPTR, # 8245H : Move the data 8245 into the data pointer register.

### Direct addressing mode:

- ✓ In the addressing mode, the data operand is in the RAM location (00 -7FH) and the address of the data operand is given in the instruction.

- ✓ The direct addressing mode uses the lower 128 bytes of Internal RAM and the SFRs

Examples:

- MOV R1, 42H : Move the contents of RAM location 42 into R1 register

- MOV 49H, A : Move the contents of the accumulator into the RAM location 49.

- ADD A, 56H : Add the contents of the RAM location 56 to the accumulator

### Register addressing mode:

$\checkmark$  In the addressing mode, the data operands are available in the registers.

Examples:

- MOV A, R0 : Move the contents of the register R0 to the accumulator

- MOV P1, R2 :Move the contents of the R2 register into port 1

- MOV R5, R2 : This is invalid. The data transfer between the registers is not allowed.

### **Register Indirect addressing mode:**

$\checkmark$  In the addressing mode, a register is used as a pointer to the data memory block.

Examples:

- MOV A,@ R0 : Move the contents of RAM location whose address is in R0 into A (accumulator)

- MOV @ R1 , B : Move the contents of B into RAM location whose address is held by R1

- When R0 and R1 are used as pointers, they must be preceded by @ sign

- ✓ Advantage: It makes accessing the data more dynamic than static as in the case of direct addressing mode.

### Indexed addressing mode:

✓ This addressing mode is used in accessing the data elements of lookup table entries, located in program ROM.

### Example: MOVC A, @ A+DPTR

The 16-bit register DPTR and register A are used to form the address of the data element stored in onchip ROM.

### **INSTRUCTIONS SET OF 8051:**

Discuss in detail the 8051 instruction set. (NOV 2008)

Arithmetic instructions:

| ET3491 EMBEDDEI | D SYSTEM AND IOT DESIGN Unit-1                                                            |

|-----------------|-------------------------------------------------------------------------------------------|

| With example, e | xplain arithmetic instructions in 8051 microcontroller. (NOV 2012)                        |

| ✓ ADD           |                                                                                           |

|                 | • 8-bit addition between the accumulator (A) and a second operand.                        |

|                 | • The result is always in the accumulator.                                                |

|                 | • The CY flag is set/reset appropriately.                                                 |

| ✓ ADDC          |                                                                                           |

|                 | • 8-bit addition between the accumulator, a second operand and the previous value of the  |

|                 | CY flag.                                                                                  |

|                 | • Useful for 16-bit addition in two steps.                                                |

|                 | • The CY flag is set/reset appropriately.                                                 |

| ✓ DAA           |                                                                                           |

|                 | • Decimal adjust the accumulator.                                                         |

|                 | • Format the accumulator into a proper 2 digit packed BCD number.                         |

|                 | • Operates only on the accumulator.                                                       |

|                 | • Works only after the ADD instruction.                                                   |

| ✓ SUBB          |                                                                                           |

|                 | Subtract with Borrow.                                                                     |

|                 | • Subtract an operand and the previous value of a borrow (carry) flag from the            |

|                 | accumulator.                                                                              |

|                 | • $A \leftarrow A - \langle \text{operand} \rangle - CY.$                                 |

|                 | • The result is always saved in the accumulator.                                          |

|                 | • The CY flag is set/reset appropriately.                                                 |

| ✓ INC           |                                                                                           |

|                 | • Increment the operand by one.                                                           |

|                 | • The operand can be a register, a direct address, an indirect address, the data pointer. |

| ✓ DEC           |                                                                                           |

|                 | • Decrement the operand by one.                                                           |

|                 | • The operand can be a register, a direct address, an indirect address.                   |

| ✓ MUL AB        | / DIV AB                                                                                  |

|                 | • Multiply A by B and place result in A and B registers.                                  |

|                 | • Divide A by B and place quotient in A register & remainder in B register.               |

• • • 9

### Logical instructions in 8051.

- ✓ ANL : It performs AND logical operation between two operands.

- ➢ Work on byte sized operands or the CY flag.

- ANL A, Rn

- ANL A, direct

- ANL A, @ Ri

- ANL A, #data

- ANL direct, A

- ANL direct, #data

- ANL C, bit

- ANL C, /bit

- ✓ ORL: It performs OR logical operation between two operands.

- ➢ Work on byte sized operands or the CY flag.

- ORL A, Rn

- ORL A, direct

- ORL A, @Ri

- ORL A, #data

✓ XRL

- ➢ Works on bytes only.

- XRL A, Rn

- XRL A, direct

- ✓ CPL/CLR

- Complement / Clear.

- $\succ$  Work on the accumulator or a bit.

- CLR P1.2

- CPL Rn

- ✓ RL / RLC / RR / RRC

- $\succ$  Rotate the accumulator.

- RL and RR without the carry

- RLC and RRC rotate through the carry.

- SWAP A: Swap the upper and lower nibbles of the accumulator.

| ET3491 EMBEDDED SYSTEM AND IOT DESIGN Unit-1                |                                   |  |

|-------------------------------------------------------------|-----------------------------------|--|

| Data transfer instructions in 8051.                         |                                   |  |

| Briefly explain the data transfer instructions available in | 8051 microcontroller . (NOV 2014) |  |

| MOV                                                         |                                   |  |

| ➢ 8-bit data transfer for internal RAM and the SFR.         |                                   |  |

| • MOV A, Rn                                                 |                                   |  |

| MOV A, direct                                               |                                   |  |

| • MOV A, @Ri                                                |                                   |  |

| • MOV A, #data                                              |                                   |  |

| • MOV Rn, A                                                 |                                   |  |

| MOV Rn, direct                                              |                                   |  |

| MOV Rn, #data                                               |                                   |  |

| • MOV direct, A                                             |                                   |  |

| MOV direct, Rn                                              |                                   |  |

| MOV direct, direct                                          |                                   |  |

| • MOV direct, @Ri                                           |                                   |  |

| • MOV direct, #data                                         |                                   |  |

| • MOV @Ri, A                                                |                                   |  |

| MOV @Ri, direct                                             |                                   |  |

| MOV @Ri, #data                                              |                                   |  |

| ✓ MOV                                                       |                                   |  |

| 1-bit data transfer involving the CY flag                   |                                   |  |

| • MOV C, bit                                                |                                   |  |

| MOV bit, C                                                  |                                   |  |

| ✓ MOV                                                       |                                   |  |

| 16-bit data transfer involving the DPTR                     |                                   |  |

| MOV DPTR, #data                                             |                                   |  |

| ✓ MOVC                                                      |                                   |  |

| Move Code Byte                                              |                                   |  |

| • Load the accumulator with a byte from prog                | ram memory.                       |  |

| • Must use indexed addressing                               |                                   |  |

| • MOVC A, @A+DPTR                                           |                                   |  |

• MOVC A, @A+PC

## ✓ MOVX

- > Data transfer between the accumulator and a byte from external data memory.

- MOVX A, @Ri

- MOVX A, @DPTR

- MOVX @Ri, A

- MOVX @DPTR, A

### ✓ PUSH / POP

- > Push and Pop a data byte onto the stack.

- > The data byte is identified by a direct address from the internal RAM locations.

- PUSH DPL

- POP 40H

### ✓ XCH

- Exchange accumulator and a byte operand

- XCH A, Rn

- XCH A, direct

- XCH A, @Ri

### ✓ XCHD

- > Exchange lower digit of accumulator with the lower digit of the memory location specified.

- XCHD A, @Ri

- The lower 4-bits of the accumulator are exchanged with the lower 4-bits of the internal memory location identified indirectly by the index register.

- The upper 4-bits of each are not modified.

### Boolean (or) Bit manipulation instructions in 8051.

- $\checkmark$  This group of instructions is associated with the single-bit operations of the 8051.

- ✓ This group allows manipulating the individual bits of bit addressable registers and memory locations as well as the CY flag.

- The P, OV, and AC flags cannot be directly altered.

- $\checkmark$  This group includes:

- Set, clear, and, or complement, move.

- Conditional jumps.

- ✓ CLR

- Clear a bit or the CY flag.

- CLR P1.1

- CLR C

## ✓ SETB

- Set a bit or the CY flag.

- SETB A.2

- SETB C

# ✓ CPL

- Complement a bit or the CY flag.

- CPL 40H; Complement bit 40 of the bit addressable memory

- ✓ ORL / ANL

- OR / AND a bit with the CY flag.

- ORL C, 20H; OR bit 20 of bit addressable memory with the CY flag

- ANL C, 34H; AND bit 34 of bit addressable memory with the CY flag.

# ✓ MOV

- Data transfer between a bit and the CY flag.

- MOV C, 3FH; Copy the CY flag to bit 3F of the bit addressable memory.

- MOV P1.2, C; Copy the CY flag to bit 2 of P1.

# ✓ JC / JNC

• Jump to a relative address if CY is set / cleared.

# ✓ JB / JNB

- Jump to a relative address if a bit is set / cleared.

- JB ACC.2, <labe⊳

- $\checkmark$  JBC Jump to a relative address, if a bit is set and clear the bit.

# **Branching instructions:**

With example, explain branching instructions in 8051 microcontroller. (May 2010, NOV 2012)

# Explain the working of program control transfer instructions of 8051. (May 2012)

- ✓ The 8051 provides four different types of unconditional jump instructions:

- ➢ Short Jump − SJMP

- Uses an 8-bit signed offset relative to the  $1^{st}$  byte of the next instruction.

- Long Jump LJMP

- Uses a 16-bit address.

13

- 3 byte instruction capable of referencing any location in the entire 64K of program memory.

- Absolute Jump AJMP

- Uses an 11-bit address.

- 2 byte instruction

- The 11-bit address is substituted for the lower 11-bits of the PC to calculate the 16-bit address of the target.

- The location referenced must be within the 2K Byte memory.

- ➢ Indirect Jump − JMP

- JMP @A + DPTR

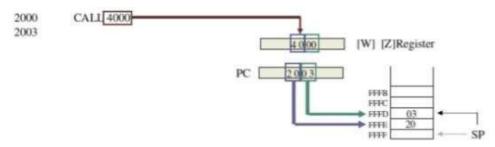

- ✓ The 8051 provides 2 forms for the CALL instruction:

- ➢ Absolute Call − ACALL

- Uses an 11-bit address similar to AJMP

- The subroutine must be within the same 2K page.

- ➢ Long Call − LCALL

- Uses a 16-bit address similar to LJMP

- The subroutine can be anywhere.

- Both forms push the 16-bit address of the next instruction on the stack and update the stack pointer.

- $\checkmark$  The 8051 provides 2 forms for the return instruction:

- Return from subroutine RET

- Pop the return address from the stack and continue execution there.

- Return from Interrupt Service Routine RETI

- Pop the return address from the stack.

- Continue execution at the address retrieved from the stack.

- The PSW is not automatically restored.

- ✓ The 8051 supports 5 different conditional jump instructions.

- > ALL conditional jump instructions use an 8-bit signed offset.

- > Jump on Zero JZ / JNZ

- Jump if the A == 0 / A != 0

- The check is done at the time of the instruction execution.

### $\blacktriangleright$ Jump on Carry – JC / JNC

- Jump if the C flag is set / cleared.

- ➤ Jump on Bit JB / JNB

- Jump if the specified bit is set / cleared.

- Any addressable bit can be specified.

- ➤ Jump if the Bit is set then Clear the bit JBC

- Jump if the specified bit is set.

- Then clear the bit.

- ✓ Compare and Jump if Not Equal CJNE

- > Compare the magnitude of the two operands and jump if they are not equal.

- The values are considered to be unsigned.

- The Carry flag is set / cleared appropriately.

- CJNE A, direct, rel

- CJNE Rn, #data, rel

- CJNE @Ri, #data, rel

- ✓ Decrement and Jump if Not Zero DJNZ

- Decrement the first operand by 1 and jump to the location identified by the second operand if the resulting value is not zero.

- DJNZ Rn, rel

- DJNZ direct, rel

- $\blacktriangleright$  NOP No operation

### Memory organization :

Explain in detail the internal memory organization of 8051 microcontroller (NOV 2014, May 2012, NOV 2011, NOV 2010, May 2010, MAY 2009, NOV 2008, NOV 2007)

- ✓ The 8051 microcontroller has 128 bytes of Internal RAM and 4kB of on chip ROM.

- ✓ The RAM is also known as Data memory and the ROM is known as program (Code) memory.

- $\checkmark$  Code memory holds the actual 8051 program to be executed.

- ✓ In 8051, memory is limited to 64KB.

- ✓ Code memory may be found on-chip, as ROM or EPROM.

- ✓ It may also be stored completely off-chip in an external ROM / EPROM.

- ✓ The 8051 has only 128 bytes of Internal RAM but it supports 64KB of external RAM.

$\checkmark$  Since the memory is off-chip, it is not as flexible for accessing and is also slower.

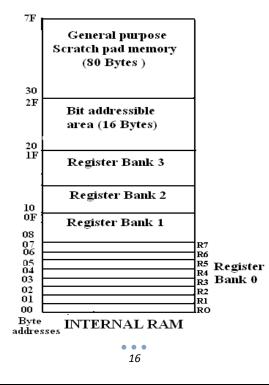

#### Structure of Internal RAM OF 8051(Data Memory) :

#### Explain the Data memory structure of 8051. (NOV 2011)

- $\checkmark$  Internal RAM is found on-chip on the 8051. So it is the fastest RAM available.

- $\checkmark$  It is flexible in terms of reading, writing and modifying its contents.

- ✓ Internal RAM is volatile.

- $\checkmark$  When the 8051 is reset, internal RAM is cleared.

- $\checkmark$  The 128 bytes of internal RAM is organized as below.

- ✓ Four register banks (Bank0, Bank1, Bank2 and Bank3) each of 8-bits (total 32 bytes).

- $\checkmark$  The default bank register is Bank0.

- ✓ The remaining Banks are selected with the help of RS0 and RS1 bits of PSW Register.

- $\checkmark$  16 bytes of bit addressable area and

- $\checkmark$  80 bytes of general purpose area (Scratch pad memory) of internal RAM as shown in the diagram below.

- $\checkmark$  This area is utilized by the microcontroller as a storage area for the operating stack.

- ✓ The 32 bytes of RAM from address 00 H to 1FH are used as working registers organized as four banks of eight registers each.

- $\checkmark$  The registers are named as R0-R7.

- $\checkmark$  Each register can be addressed by its name or by its RAM address.

For example: MOV A, R7 or MOV R7,#05H

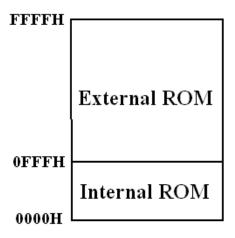

### Structure of Internal ROM (On -chip ROM / Program Memory / Code Memory):

- ✓ The 8051 microcontroller has 4KB of on chip ROM, but it can be extended up to 64KB.

- ✓ This ROM is also called program memory or code memory.

- ✓ The CODE segment is accessed using the program counter (PC) for opcode fetches and by DPTR for data.

- ✓ The external ROM is accessed when the EA pin is connected to ground or the contents of program counter exceeds 0FFFH.

- ✓ When the Internal ROM address is exceeded the 8051 automatically fetches the code bytes from the external program memory.

### SPECIAL FUNCTION REGISTERS (SFRs)

Write the available special function registers in 8051. Explain each register with its format and functions. (April 2017, NOV 2015)

- ✓ In 8051 microcontroller, there are registers which uses the RAM addresses from 80h to FFh.

- ✓ They are used for certain specific operations. These registers are called Special Function Registers (SFRs).

- $\checkmark$  Most of SFRs are bit addressable and other few registers are byte addressable.

- ✓ In these SFRs, some of them are related to I/O ports (P0, P1, P2 and P3) and some of them are for control operations (TCON, SCON & PCON).

- ✓ Remaining are the auxiliary SFRs, that they don't directly configure the 8051.

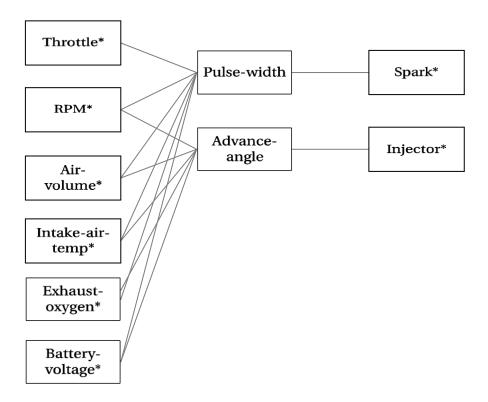

- $\checkmark$  The list of SFRs and their functional names are given below.

- ✓ The <sup>\*</sup> indicates the bit addressable SFRs

| S.No | Symbol |      | Name of SFR                  | Address (Hex) |  |

|------|--------|------|------------------------------|---------------|--|

| 1    | ACC*   |      | Accumulator                  | 0E0           |  |

| 2    |        | B*   | B-Register                   | <b>0F0</b>    |  |

| 3    |        | PSW* | Program Status word register | 0DO           |  |

| 4    |        | SP   | Stack Pointer Register       | 81            |  |

| 5    |        | DPL  | Data pointer low byte        | 82            |  |

|      | DPTR   | DPH  | Data pointer high byte       | 83            |  |

| 6    |        | P0*  | Port 0                       | 80            |  |

|      |        | P1*  | Port 1                       | 90            |  |

| 8    |        | P2*  | Port 2                       | 0A            |  |

| 9    | P3*    |      | Port 3                       | 0B            |  |

| 10   | IP*    |      | Interrupt Priority control   | 0B8           |  |

| 11   | IE*    |      | Interrupt Enable control     | 0A8           |  |

| 12   | TMOD   |      | Timer mode register          | 89            |  |

| 13   | TCON*  |      | Timer control register       | 88            |  |

| 14   |        | TH0  | Timer 0 Higher byte          | 8C            |  |

| 15   |        | TL0  | Timer 0 Lower byte           | 8A            |  |

| 16   | TH1    |      | Timer 1 Higher byte          | 8D            |  |

| 17   | TL1    |      | Timer 1 lower byte           | 8B            |  |

| 18   | SCON*  |      | Serial control register      | 98            |  |

| 19   | SBUF   |      | Serial buffer register       | 99            |  |

| 20   |        | PCON | Power control register       | 87            |  |

### **Table: Special Function Registers**

### STACK in 8051 Microcontroller:

- $\checkmark$  The stack is a part of RAM used by the CPU to store information temporarily.

- $\checkmark$  This information may be either data or an address.

- $\checkmark$  The register used to access the stack is called the Stack pointer (SP).

- $\checkmark$  SP is an 8-bit register. So, it can take values of 00 to FF H.

- ✓ When the 8051 is powered up, the SP register contains the value 07.i.e the RAM location value 08 is the first location being used for the stack by the 8051 controller.

- $\checkmark$  There are two important instructions to handle stack. One is the PUSH and the other is the POP.

- $\checkmark$  The loading of data from CPU registers to the stack is done by PUSH.

- $\checkmark$  The loading of the contents of the stack back into a CPU register is done by POP.

# Interrupts:

# Explain interrupt structure of 8051 microcontroller. (NOV 2011, MAY 2009)

# Interrupt Structure:

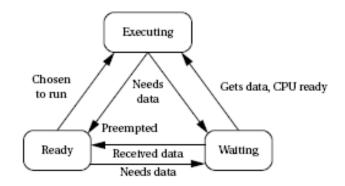

- ✓ An interrupt is an external or internal event that disturbs the microcontroller to inform it that a device needs its service.

- ✓ The program which is associated with the interrupt is called the interrupt service routine (ISR) or interrupt handler.

- ✓ Upon receiving the interrupt signal, the microcontroller finishes current operation and saves the PC on stack.

- ✓ Jumps to a fixed location in memory depending on type of interrupt.

- ✓ Starts to execute the interrupt service routine until RETI.

- ✓ Upon executing the RETI the microcontroller returns to the place where it was interrupted. Get pop PC from stack.

- $\checkmark$  The 8051 microcontroller has **FIVE** interrupts in addition to Reset. They are

- Timer 0 overflow Interrupt

- Timer 1 overflow Interrupt

- External Interrupt 0(INT0)

- External Interrupt 1(INT1)

- Serial Port Interrupt

- $\checkmark$  Each interrupt has a specific place in code memory where program execution begins.

- External Interrupt 0: 0003 H

- Timer 0 overflow: 000B H

- External Interrupt 1: 0013 H

- Timer 1 overflow: 001B H

- Serial Interrupt : 0023 H

- ✓ Upon reset all Interrupts are disabled & do not respond to the Microcontroller.

- ✓ These interrupts must be enabled by software. This is done by an 8-bit register called Interrupt Enable Register (IE).

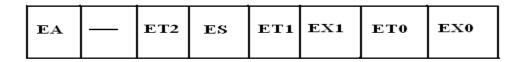

### Interrupt Enable Register :

- EA : Global enable/disable. To enable the interrupts, this bit must be set high.

- --- : Undefined-reserved for future use.

- ET2 : Enable /disable Timer 2 overflow interrupt.

- ES : Enable/disable Serial port interrupts.

- ET1 : Enable /disable Timer 1 overflow interrupt.

- EX1 : Enable/disable External interrupt1.

- ET0 : Enable /disable Timer 0 overflow interrupt.

- EX0 : Enable/disable External interrupt0

- ✓ Upon reset, the interrupts have the following priority from top to down. The interrupt with the highest PRIORITY gets serviced first.

- 1. External interrupt 0 (INT0)

- 2. Timer interrupt0 (TF0)

- 3. External interrupt 1 (INT1)

- 4. Timer interrupt1 (TF1)

- 5. Serial communication (RI+TI)

- ✓ Priority can also be set to "high" or "low" by 8-bit IP register.

### Interrupt priority register:

| PT2 | PS | PT1 | PX1 | рто | PX0 |

|-----|----|-----|-----|-----|-----|

|-----|----|-----|-----|-----|-----|

- IP.7: reserved

- IP.6: reserved

- IP.5: Timer 2 interrupt priority bit (8052 only)

- IP.4: Serial port interrupt priority bit

- IP.3: Timer 1 interrupt priority bit

- IP.2: External interrupt 1 priority bit

- IP.1: Timer 0 interrupt priority bit

- IP.0: External interrupt 0 priority bit

### **PROGRAMMING TIMERS OF 8051**

Explain the different modes of operation of time rs in 8051 in detail with its associated registers. Describe different modes of operation of time rs /counters in 8051 with its associated registers. (NOV 2009, MAY 2009. May 2007, May 2016)

Draw and explain the functions of TCON and TMOD registers of 8051. (Dec 2008) Explain the on-chip timer modes of an 8051 Microcontroller. (April 2010, NOV 2016)

### Timer Registers.

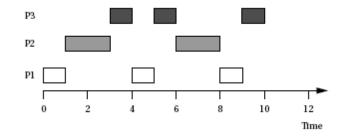

$\checkmark$  The 8051 has two timers/counters, they can be used either as timers (used to generate a time delay) or as event counters.

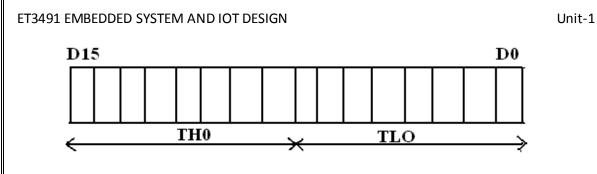

### TIMER 0:

- $\checkmark$  Timer 0 is a 16-bit register and can be treated as two 8-bit registers (TL0 & TH0).

- ✓ These registers can be accessed similar to any other registers like A, B or R1 etc

- ✓ Ex : The instruction MOV TL0,#07 moves the value 07 into lower byte of Timer0.

- ✓ Similarly MOV R1, TH0 saves the contents of TH0 in the R1 register.

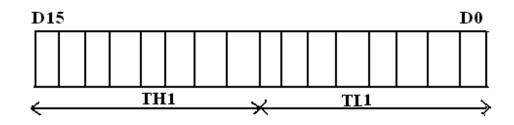

### TIMER 1:

- ✓ Timer 1 is also a 16-bit register and can be treated as two 8-bit registers (TL1 & TH1).

- ✓ These registers can be accessed similar to any other registers like A, B or R1etc

- $\checkmark$  Ex : The instruction MOV TL1,#05 moves the value 05 into lower byte of Timer1.

- ✓ Similarly MOV R0,TH1 saves the contents of TH1 in the R0 register.

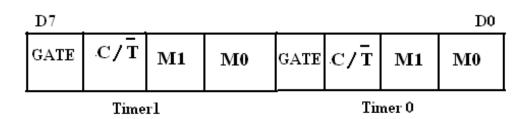

#### TMOD (Timer mode Register):

- $\checkmark$  The various operating modes of both the timers T0 and T1 are set by a TMOD register.

- $\checkmark$  TMOD is a 8-bit register.

- ✓ The lower 4 bits are for Timer 0

- $\checkmark$  The upper 4 bits are for Timer 1

- ✓ In each case,

- The lower 2 bits are used to set the timer mode

- The upper 2 bits to specify the operation

#### Unit-1

### GATE:

- $\checkmark$  This bit is used to start or stop the timers by hardware.

- $\checkmark$  When GATE= 1, the timers can be started / stopped by the external sources.

- ✓ When GATE= 0, the timers can be started or stopped by software instructions like SETB TR<sub>X</sub> or CLR TR<sub>X</sub>.

### C/T (Counter/Timer):

- $\checkmark$  This bit decides whether the timer is used as delay generator or event counter.

- ✓ When  $C/\overline{T} = 0$ , timer is used as delay generator.

- ✓ When  $C/\overline{T} = 1$ , timer is used as an event counter.

- $\checkmark$  The clock source for the time delay is the crystal frequency of 8051.

- $\checkmark$  The clock source for the event counter is the external clock source.

### M1, M0 (Mode):

- $\checkmark$  These two bits are the timer mode bits.

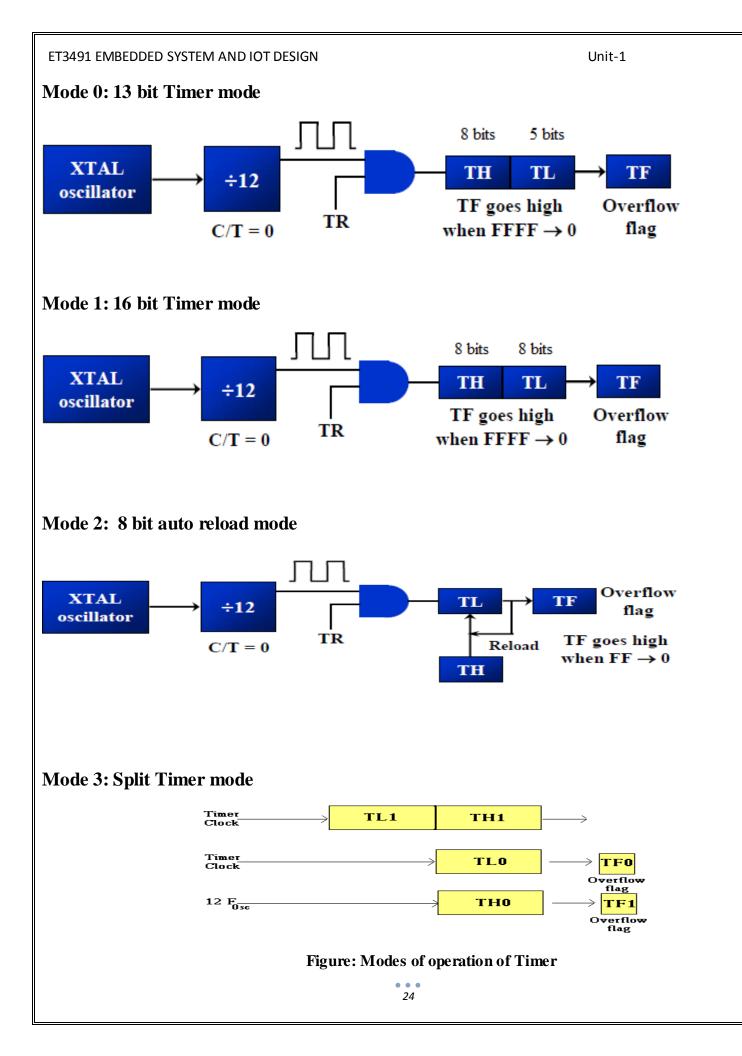

- ✓ The timers of the 8051 can be configured in four modes Mode0, Mode1, Mode2 & Mode 3.

- $\checkmark$  The selection and operation of the modes is shown below.

| S.No | <b>M0</b> | M1 | Mode   | Operation                                                                                                                         |

|------|-----------|----|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| 1    | 0         | 0  | Mode 0 | <ul><li>13-bit Timer mode.</li><li>8-bit Timer/counter THx with TLx as 5-bit prescaler</li></ul>                                  |

| 2    | 0         | 1  | Mode 1 | <b>16-bit Timer mode</b> .16-bit timer /counter<br>THx and TLx are cascaded. There is no<br>presacler                             |

| 3    | 1         | 0  | Mode 2 | 8-bit auto reload.<br>8-bit auto reload timer/counter. THx holds a<br>value which is to be reloaded TLx each time<br>it overflows |

| 4    | 1         | 1  | Mode 3 | Split timer mode                                                                                                                  |

| ET3491 EME |             | EM AND IOT DES                                                       | IGN               |                 |                 | Unit-1          |               |  |

|------------|-------------|----------------------------------------------------------------------|-------------------|-----------------|-----------------|-----------------|---------------|--|

| TCON (Ti   | mer control | register)                                                            |                   |                 |                 |                 |               |  |

|            |             | ontrol) register                                                     | is an 8-bit reg   | sister. TCON    | register is a b | oit-addressab   | le register.  |  |

| 7          | 6           | 5                                                                    | 4                 | 3               | 2               | 1               | 0             |  |

| TF1        | TR1         | TF0                                                                  | TRO               | IE1             | IT1             | IEO             | ITO           |  |

|            |             |                                                                      |                   |                 |                 |                 |               |  |

| Bit        | Bit         |                                                                      |                   | Descri          | ption           |                 |               |  |

| Number     | Mnemonic    |                                                                      |                   |                 |                 |                 |               |  |

| 7          | TF1         | Timer 1 overf                                                        | low flag          |                 |                 |                 |               |  |

|            |             | Cleared by ha                                                        | rdware when       | processor ve    | ctors to intern | upt routine.    |               |  |

|            |             | Set by hardwa                                                        | re on timer/co    | ounter overfl   | ow, when the    | timer 1 regis   | ter overflows |  |

| 6          | TR1         | Timer 1 run c                                                        | ontrolbit         |                 |                 |                 |               |  |

|            |             | Clear to turn of                                                     | off time/count    | er 1.           |                 |                 |               |  |

|            |             | Set to turn on                                                       | timer/counter     | :1.             |                 |                 |               |  |

| 5          | TF0         | Timer 0 overf                                                        | low flag          |                 |                 |                 |               |  |

|            |             | Cleared by hardware when processor vectors to interrupt routine.     |                   |                 |                 |                 |               |  |

|            |             | Set by hardware on timer/counter overflow, when the timer 0 register |                   |                 |                 |                 |               |  |

| 4          | TR0         | Timer 0 run c                                                        | ontrol bit        |                 |                 |                 |               |  |

|            |             | Clear to turn of                                                     | off time/count    | er 0.           |                 |                 |               |  |

|            |             | Set to turn on                                                       | timer/counter     | : 0.            |                 |                 |               |  |

| 3          | IE1         | External inter                                                       | rupt 1 edge fl    | ag.             |                 |                 |               |  |

|            |             | Cleared by ha                                                        | rdware when       | interrupt is p  | rocessed if ea  | lge-triggered   |               |  |

|            |             | Set by hardwa                                                        | are when extended | rnal interrupt  | is detected o   | n INT1 pin.     |               |  |

| 2          | IT1         | External inter                                                       | rupt 1 type co    | ntrolbit        |                 |                 |               |  |

|            |             | Clear to selec                                                       | t low level act   | tive (level tri | ggered) for ex  | xternal interru | ıpt 1.        |  |

|            |             | Set to select fa                                                     | alling edge ac    | tive (edge tri  | ggered) for e   | xternal interr  | upt 1.        |  |

| 1          | IEO         | External inter                                                       | rupt 0 ed ge fl   | ag              |                 |                 |               |  |

|            |             | Cleared by ha                                                        | rdware when       | interrupt is p  | rocessed if ed  | dge-triggered   |               |  |

|            |             | Set by hardwa                                                        | are when extended | rnal interrupt  | is detected o   | n INT0 pin.     |               |  |

| 0          | IT0         | External inter                                                       | rupt 0 type co    | ntrolbit        |                 |                 |               |  |

|            |             | Clear to selec                                                       | t low level act   | tive (level tri | ggered) for ex  | xternal interru | upt 0.        |  |

|            |             | Set to select fa                                                     |                   |                 |                 |                 |               |  |

### Timers of 8051 do starting and stopping by either software or hardware control

- $\checkmark$  For using software to start and stop the timer where GATE=0

- $\checkmark$  The start and stop of the timer are controlled by software using TR (timer start) bits TR<sub>X</sub> and CLR<sub>X</sub>

- $\checkmark$  The SETB instruction starts it, and it is stopped by the CLR instruction.

- $\checkmark$  These instructions start and stop the timers as long as GATE=0 in the TMOD register

- ✓ The hardware way of starting and stopping the timer is achieved by making GATE=1 in the TMOD register.

# The following are the characteristics and operations of mode 1:

- 1. It is a 16-bit timer.

- 2. It allows value from 0000 to FFFFH.

- 3. Value to be loaded into the timer register TL and TH.

- 4. After TH and TL are loaded with a 16-bit initial value, the timer must be started

- This is done by SETB TR0 for timer 0 and SETB TR1 for timer 1

- 5. After the timer is started, it starts to count up

- It counts up until it reaches its limit of FFFFH

- When it rolls over from FFFFH to 0000, it sets high a flag bit called TF (timer flag)

Unit-1

- Each timer has its own timer flag.

- There are TF0 for timer 0, and TF1 for timer 1.

- 6. Timer flag can be monitored,

- When this timer flag is raised, to stop the timer with the CLR instructions.

- CLR TR0 and CLR TR1, for timer 0 and timer 1 respectively.

- After the timer reaches its limit and rolls over.

- In order to repeat the process, TH and TL must be reloaded with the original value and TF must be reloaded to 0.

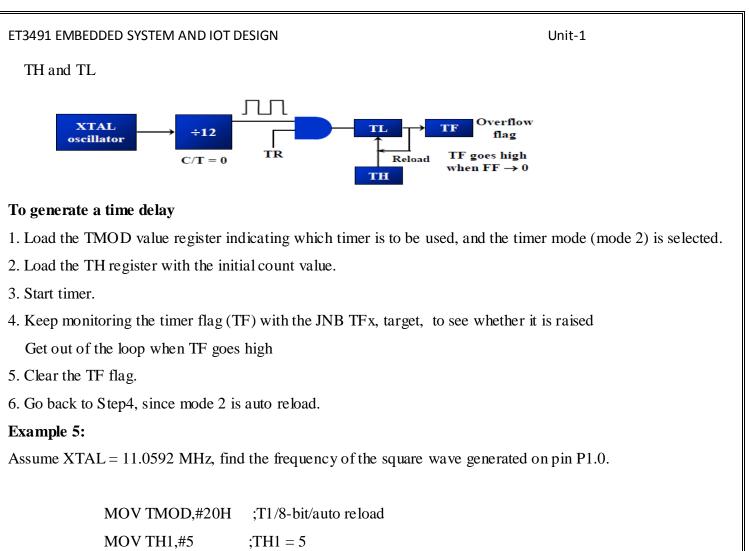

# To generate a time delay

- 1. Load the TMOD register indicating which timer is to be used and which timer mode is selected.

- 2. Load registers TL and TH with initial count value.

- 3. Start the timer

- 4. Keep monitoring the timer flag (TF) with the JNB TFx, target to see if it is raised

- Get out of the loop when TF becomes high

- 5. Stop the timer

- 6. Clear the TF flag for the next round

7. Go back to Step 2 to load TH and TL again.

# Example 1:

In the following program, we create a square wave of 50% duty cycle (with equal portions high and low) on the P1.5 bit. Timer 0 is used to generate the time delay. Analyze the program. (Nov 2014)

|        | MOV TMOD,#01   | ;Timer 0, mode 1(16-bit mode)             |

|--------|----------------|-------------------------------------------|

| HERE:  | MOV TL0,#0F2H  | ;TL0=F2H, the low byte                    |

|        | MOV TH0,#0FFH  | ;TH0=FFH, the high byte                   |

|        | CPL P1.5       | ;toggle P1.5                              |

|        | ACALL DELAY    |                                           |

|        | SJMP HERE      |                                           |

| DELAY: | SETB TR0       | ;start the timer 0                        |

| AGAIN: | JNB TF0, AGAIN | ;monitor timer flag 0 until it rolls over |

|        | CLR TR0        | ;stop timer 0                             |

|        | CLR TF0        | ;clear timer 0 flag                       |

|        | RET            |                                           |

In the above program notice the following steps.

- 1. TMOD is loaded.

- 2. FFF2H is loaded into TH0-TL0.

- 3. P1.5 is toggled for the high and low portions of the pulse.

- 4. The DELAY subroutine using the timer is called.

- 5. In the DELAY subroutine, timer 0 is started by the SETB TR0 instruction.

- 6. Timer 0 counts up with the passing of each clock, which is provided by the crystal oscillator.

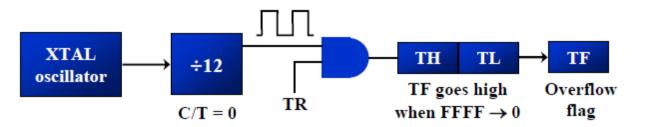

- As the timer counts up, it goes through the states of FFF3, FFF4, FFF5, FFF6, and so on until it reaches FFFFH.

- One more clock rolls it to 0, raising the timer flag (TF0=1). At that point, the JNB instruction falls through.

7. Timer 0 is stopped by the instruction CLR TR0.

• The DELAY subroutine ends and the process is repeated.

Notice that to repeat the process, we must reload the TL and TH registers, and start the process is repeated.

# In Example 1, calculate the amount of time delay in the DELAY subroutine generated by the timer. Assume XTAL = 11.0592 MHz.

### Solution:

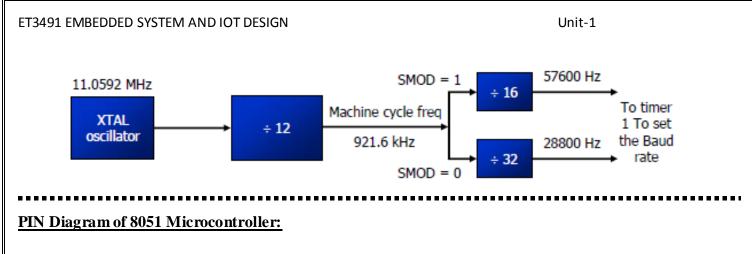

- ✓ The timer works with a clock frequency of 1/12 of the XTAL frequency, we have 11.0592 MHz / 12 = 921.6 kHz as the timer frequency.

- ✓ As a result, each clock has a period of T =1/921.6kHz,T=1.085µs.

- ✓ In other words, Timer 0 counts up each 1.085 µs resulting in delay = number of counts  $\times$  1.085 µs.

- ✓ The number of counts for the roll over is FFFFH FFF2H = 0DH (13 decimal).

- $\checkmark$  Add one to 13 because of the extra clock needed when it rolls over from FFFF to 0 and raise the TF flag.

- ✓ This gives  $14 \times 1.085 \,\mu\text{s} = 15.19 \,\mu\text{s}$  for half the pulse. For the entire period it is T = 2 × 15.19  $\mu\text{s} = 30.38 \,\mu\text{s}$  as the time delay generated by the timer.

### (a) In hexadecimal

(FFFF – YYXX + 1) ×1.085  $\mu$ s, where YYXX are TH, TL initial values respectively. Notice that value YYXX are in hex.

### (b) In decimal

Convert YYXX values of the TH, TL register to decimal to get a NNNN decimal, then (65536 - NNNN)  $\times$  1.085  $\mu s$

### Example 3:

### In Example 1, calculate the frequency of the square wave generated on pin P1.5.

### Solution:

- ✓ In the timer delay calculation of Example 1, we did not include the overhead due to instruction in the loop.

- $\checkmark$  To get a more accurate timing, we need to add clock cycles due to these instructions in the loop.

- $\checkmark$  To do that, we use the machine cycle as shown below.

|       |               | Cycles |

|-------|---------------|--------|

| HERE: | MOV TL0,#0F2H | 2      |

|       | MOV TH0,#0FFH | 2      |

|       | CPL P1.5      | 1      |

|       | ACALL DELAY   | 2      |

|       | SJMP HERE     | 2      |

|       |               | • • •  |

#### ET3491 EMBEDDED SYSTEM AND IOT DESIGN

| DELAY: | SETB TR0       | 1  |

|--------|----------------|----|

| AGAIN: | JNB TF0, AGAIN | 14 |

|        | CLR TR0        | 1  |

|        | CLR TF0        | 1  |

|        | RET            | 2  |

|        | Total          | 28 |

$T=2\times 28\times 1.085$  us = 60.76  $\mu s$  and F=16458.2~Hz

### Example 4:

Find the delay generated by timer 0 in the following code, using both of the Methods. Do not include the overhead due to instruction.

|        | CLR P2.3       | ;Clear P2.3               |

|--------|----------------|---------------------------|

|        | MOV TMOD,#01   | ;Timer 0, 16-bitmode      |

| HERE:  | MOV TL0,#3EH   | ;TL0=3Eh, the low byte    |

|        | MOV TH0,#0B8H  | ;TH0=B8H, the high byte   |

|        | SETB P2.3      | ;SET high timer 0         |

|        | SETB TR0       | ;Start the timer 0        |

| AGAIN: | JNB TF0, AGAIN | ;Monitor timer flag 0     |

|        | CLR TR0        | ;Stop the timer 0         |

|        | CLR TF0        | ;Clear TF0 for next round |

|        | CLR P2.3       |                           |

### Solution:

(FFFFH-B83E+1)=47C2H=18370 in decimal and  $18370\times 1.085~\mu s=19.93145~ms$

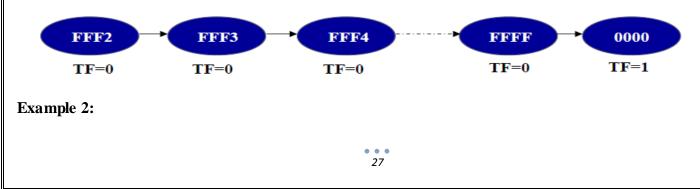

### The following are the characteristics and operations of mode 2:

1. It is an 8-bit timer. It allows only values of 00 to FFH to be loaded into the timer register TH.

2. After TH is loaded with the 8-bit value, the 8051 copies value to TL register.

- Then the timer must be started.

- This is done by the instruction SETB TR0 for timer 0 and SETB TR1 for timer 1.

3. After the timer is started, it starts to count up by incrementing the TL register.

- It counts up until it reaches its limit of FFH

- When it rolls over from FFH to 00, it sets high the TF (timer flag)

- When the TL register rolls from FFH to 00 and TF is set to 1.

- TL is reloaded automatically with the original value kept by the TH register.

- To repeat the process, simply clear TF.

4. This makes mode 2 an auto-reload, in contrast with mode 1 in which the programmer has to reload

|       | ,            | ,                      |

|-------|--------------|------------------------|

|       | SETB TR1     | ;start the timer 1     |

| BACK: | JNB TF1,BACK | ;till timer rolls over |

|       | CPL P1.0     | ;P1.0 to hi, lo        |

|       | CLR TF1      | ;clear Timer 1 flag    |

|       | SJMP BACK    | ;mode 2 is auto-reload |

### Solution:

- $\checkmark$  In mode 2, no need to reload TH since it is auto-reload.

- ✓ Now (256 05) × 1.085  $\mu$ s =251 × 1.085  $\mu$ s = 272.33  $\mu$ s is the high portion of the pulse.

- $\checkmark$  Since it is a 50% duty cycle square wave, the period T is twice.

- ✓ As a result T =  $2 \times 272.33$  µs = 544.67 µs and the frequency = 1.83597 kHz

# **5.2:** Timers as counters

Timers can also be used as counters.

Which are used for counting events happening outside the 8051.

Unit-1

- When it is used as a counter, it is a pulse outside of the 8051 that increments the TH, TL register.

- TMOD and TH, TL registers are the same as in timer concept, except the source of the frequency.

- The C/T bit in the TMOD register decides the source of the clock for the timer

- When C/T = 1, the timer is used as a counter and gets its pulses from outside the 8051.

- The counter counts up as pulses are fed from pins 14 and 15.

- these pins are called T0 (timer 0 input) and T1 (timer 1 input)

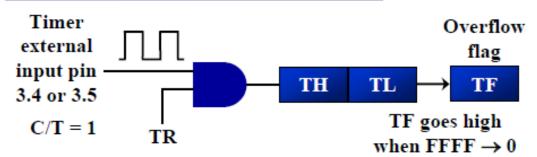

# Timer with external input (Mode 1)

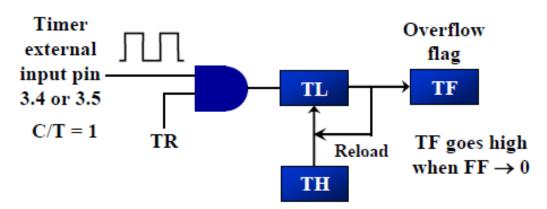

# Timer with external input (Mode 2)

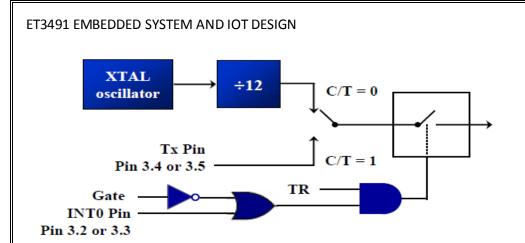

- ✓ If GATE = 1, the start and stop of the timer are done externally through pins P3.2 and P3.3 for timers 0 and 1, respectively

- $\checkmark$  This hardware allows starting or stopping the timer externally at any time via a simple switch

$\checkmark$  The frequency for the timer is always 1/12th the frequency of the crystal attached to the 8051.

Unit-1

| Port 3 pins used for Timers 0 and 1 |          |          |                                |  |

|-------------------------------------|----------|----------|--------------------------------|--|

| Pin                                 | Port Pin | Function | Description                    |  |

| 14                                  | P3.4     | Т0       | Timer/counter 0 external input |  |

| 15                                  | P3.5     | T1       | Timer/counter 1 external input |  |

### Example 6:

Assuming that clock pulses are fed into pin T1, write a program for counter 1 in mode 2 to count the pulses and display the state of the TL1 count on P2, which connects to 8 LEDs.

### Solution:

|        | MOV TM0D,#01100000B | ;counter 1, mode 2, C/T=1 external pulses |

|--------|---------------------|-------------------------------------------|

|        | MOV TH1,#0          | ;clear TH1                                |

|        | SETB P3.5           | ;make T1 input                            |

| AGAIN: | SETB TR1            | ;start the counter                        |

| BACK:  | MOV A,TL1           | ;get copy of TL                           |

|        | MOV P2,A            | ;display it on port 2                     |

|        | JNB TF1,Back        | ;keep doing, if $TF = 0$                  |

|        | CLR TR1             | ;stop the counter 1                       |

|        | CLR TF1             | ;make TF=0                                |

|        | SJMP AGAIN          | ;keep doing it                            |

|        |                     |                                           |

$\checkmark$  Notice in the above program the role of the instruction SETB P3.5.

$\checkmark$  Since ports are set up for output when the 8051 is powered up.

$\checkmark$  So, we make P3.5 an input port by making it high.

✓ In other words, we must configure (set high) the T1 pin (pin P3.5) to allow pulses to be fed into it.

## **5.3: SERIAL COMMUNICATION**

2. Explain the serial programming of 8051 with its associated registers. (May 2014, 2013)(Or)

Explain how to program for sending and receiving data serially using 8051 (April 2010, 2011)

Explain 8051 serial port programming with examples. (May 2016, NOV 2012)

Explain the serial modes of operation of 8051 microcontroller. (May 2007)

### RS232

- $\checkmark$  It is an interfacing standard RS232.

- $\checkmark$  It was set by the Electronics Industries Association (EIA) in 1960.

- $\checkmark$  The standard was set long before the advent of the TTL logic family.

- ✓ Its input and output voltage levels are not TTL compatible.

- ✓ In RS232, a 0 is represented by -3 to -25 V, while a 1 bit is +3 to +25 V.

- $\checkmark\,$  IBM introduced the DB-9 version of the serial I/O standard.

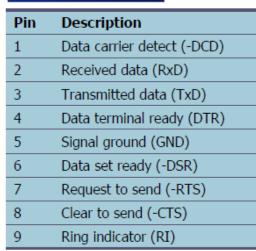

### RS232 DB-9 Pins

### Handshake signals of MODEM

### DTR (data terminal ready)

• When DTR =1, indicate that it is ready for communication.

### DSR (data set ready)

• When DSR =1, indicate that it is ready for communication.

### **RTS** (request to send)

• It asserts RTS to signal the modem that it has a byte of data to transmit.

## CTS (clear to send)

• It is to receive, it sends out signal CTS,

## DCD (data carrier detect)

• The modem asserts signal DCD to inform the DTE that a valid carrier has been detected.

# **RI** (ring indicator)

• An output from the modem and an input to a PC indicates that the telephone is ringing.

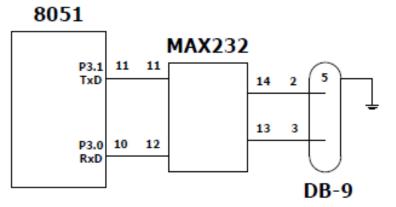

# MAX232

A line driver (MAX232) is required to convert RS232 voltage levels to TTL levels, and vice versa.

- 8051 has two pins that are used specifically for transferring and receiving data serially.

- These two pins are called TxD and RxD and are part of the port 3 (P3.0 and P3.1).

- These pins are TTL compatible.

- They require a line driver to make them RS232 compatible.

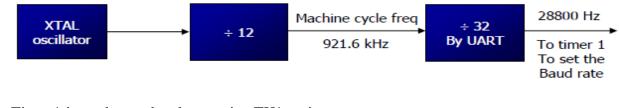

# Baud rate:

- The baud rates in 8051 are programmable.

- 8051 divides the crystal frequency by 12 to get machine cycle frequency.

- 8051 UART circuitry divides the machine cycle frequency by 32.

• Timer 1 is used to set baud rate using TH1 register

Unit-1

| Baud rate | TH1 (decimal) | TH1(Hex) |

|-----------|---------------|----------|

| 9600      | -3            | FD       |

| 4800      | -6            | FA       |

| 2400      | -12           | F4       |

| 1200      | -24           | E8       |

# Explain in detail the serial communication registers of the 8051. (NOV 2009)

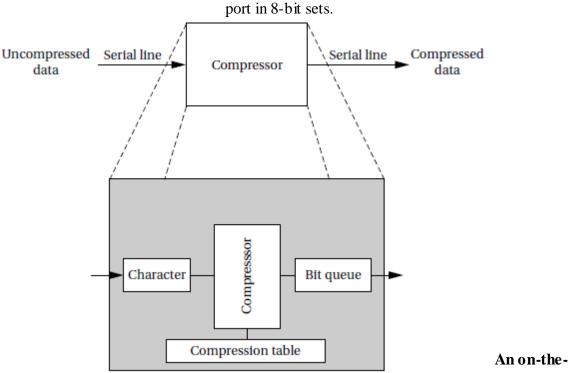

# **SBUF:**

- It is an 8-bit register used for serial communication.

- For a byte data to be transferred via the TxD line:

- Byte must be placed in the SBUF register.

- Bytes are framed with the start and stop bits and transferred serially via the TxD line.

- SBUF holds the byte of data when it is received by 8051 RxD line.

- When the bits are received serially via RxD.

- 8051 de-frames byte by eliminating the stop and start bits.

## SCON:

• It is an 8-bit register used to program the start bit, stop bit and data bits of data framing.

| SM0 | SM1 | SM2 | REN | TB8 | RB8 | TI | RI |

|-----|-----|-----|-----|-----|-----|----|----|

|     |     |     |     |     |     |    |    |

| Bit    | Bit      | Description                                                                   |

|--------|----------|-------------------------------------------------------------------------------|

| Number | Mnemonic |                                                                               |

| SCON.7 | SM0      | Serial port mode specifier                                                    |

| SCON.6 | SM1      | Serial port mode specifier                                                    |

| SCON.5 | SM2      | Used for multiprocessor communication                                         |

| SCON.4 | REN      | Set/Cleared by software to enable/disable reception                           |

| SCON.3 | TB8      | Not widely used                                                               |

| SCON.2 | RB8      | Not widely used                                                               |

| SCON.1 | TI       | Transmit interrupt flag. Set by hardware at the begin of the stop bit mode 1. |

|        |          | And cleared by software                                                       |

| SCON.0 | RI       | Receive interrupt flag. Set by hardware at the begin of the stop bit mode 1.  |

|        |          | And cleared by software                                                       |

| ET3491 EM   | IBEDDED SY    | STEM AND IOT D     | ESIGN                         | Unit-1                                         |

|-------------|---------------|--------------------|-------------------------------|------------------------------------------------|

| SM0, SM     | 1: Serial p   | ort mode speci     | fiers                         |                                                |

| SM0         | SM1           |                    |                               |                                                |

| 0           | 0             | Serial Mode 0      | 1                             |                                                |

| 0           | 1             | Serial Mode 1      | ; 8-bit data, 1 stop bit, 1 s | start bit                                      |

| 1           | 0             | Serial Mode 2      |                               |                                                |

| 1           | 1             | Serial Mode 3      |                               |                                                |

| In progra   | mming th      | e 8051 to trans    | fer character bytes seria     | lly                                            |

| 1. TMOD     | register is   | loaded with the    | value 20H, indicating the     | e use of timer 1 in mode 2 (8-bit auto-        |

| reload)     | to set bau    | d rate.            |                               |                                                |

| 2. The TH   | 1 is loaded   | l with one of the  | e values to set baud rate for | or serial data transfer.                       |

| 3. The SC   | ON registe    | r is loaded with   | the value 50H, indicating     | g serial mode 1, where an 8-bit data is framed |

|             | rt and stop   |                    |                               |                                                |

| 4. TR1 is s | set to 1 to s | start timer 1      |                               |                                                |

|             | •             | LR TI instructio   |                               |                                                |

|             | -             |                    | ed serially is written into S |                                                |

|             | U             |                    | he use of instruction JNB     | B TI, xx, to see if the character has been     |

| transfer    | rred comple   | etely.             |                               |                                                |

| 8. To trans | sfer the nex  | xt byte, go to ste | ep 5.                         |                                                |

| Write a pr  | ogram for     | the 8051 to tra    | nsfer letter "A" serially a   | at 4800 baud, continuously.                    |

| Solution:   |               |                    |                               |                                                |

|             | MOV           | TMOD, #20H         | ;timer 1, mode 2 (auto re     | eload)                                         |

|             | MOV           | TH1, #-6           | ;4800 baud rate               |                                                |

|             | MOV           | SCON, #50H         | ;8-bit, 1 stop, REN enab      | led                                            |

|             | SETB          | 5 TR1              | ;start timer 1                |                                                |

| AGAIN:      | MOV           | SBUF, #"A"         | ; letter "A" to trtansfer     |                                                |

| HERE:       | JNB           | TI, HERE           | ;wait for the last bit        |                                                |

|             | CLR           | TI                 | ;clear TI for next char       |                                                |

|             | SJMP          | 'AGAIN             | ;keep sending A               |                                                |

| The steps   | that 8051     | goes through i     | n transmitting a charact      | ter via TxD                                    |

••• 36

#### ET3491 EMBEDDED SYSTEM AND IOT DESIGN

#### Unit-1

- 1. The byte character to be transmitted is written into the SBUF register

- 2. The start bit is transferred

- 3. The 8-bit character is transferred on bit at a time

- 4. The stop bit is transferred

- It is during the transfer of the stop bit that 8051 raises the TI flag, indicating that the last character was transmitted

- 5. By monitoring the TI flag, we make sure that we are not overloading the SBUF

- If we write another byte into the SBUF before TI is raised, the un-transmitted portion of the previous byte will be lost.

6. After SBUF is loaded with a new byte, the TI flag bit must be forced to 0 by CLR TI in order for this new byte to be transferred

By checking the TI flag bit, we know whether or not the 8051 is ready to transfer another byte

- It must be noted that TI flag bit is raised by 8051 itself when it finishes data transfer

- It must be cleared by the programmer with instruction CLR TI

- If we write a byte into SBUF before the TI flag bit is raised, we risk the loss of a portion of the byte being transferred

- The TI bit can be checked by the instruction JNB TI, xx Using an interrupt.

Write a program for the 8051 to transfer "YES" serially at 9600 baud, 8-bit data, 1 stop bit do this continuously. (May 2006)

#### Solution:

|        | MOV  | TMOD, #20H | ;timer 1, mode 2   | (auto reload) |

|--------|------|------------|--------------------|---------------|

|        | MOV  | TH1, #-3   | ;9600 baud rate    |               |

|        | MOV  | SCON, #50H | ;8-bit, 1 stop, RE | EN enabled    |

|        | SETB | TR1        | ;start timer 1     |               |

| AGAIN: | MOV  | A, # "Y"   | ;transfer "Y"      |               |

|        | ACAL | L TRANS    |                    |               |

|        | MOV  | A, # "E"   | ;transfer "E"      |               |

|        | ACAL | L TRANS    |                    |               |

|        | MOV  | A, # "S"   | ;transfer "S"      |               |

|        | ACAL | L TRANS    |                    |               |

|        |      |            |                    | • • •         |

| ET3491 EMBEDDED SYSTEM AND IOT DESIGN                                                                    |                                            | DESIGN           | Unit-1                                          |                                  |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------|-------------------------------------------------|----------------------------------|

|                                                                                                          | SJMP                                       | AGAIN            | ;keep doing it                                  |                                  |

| ;serial data tr                                                                                          | ansfer s                                   | ubroutine        |                                                 |                                  |

| TRANS:                                                                                                   | MOV                                        | SBUF, A          | ;load SBUF                                      |                                  |

| HERE:                                                                                                    | JNB                                        | TI, HERE         | ;wait for the last bit                          |                                  |

|                                                                                                          | CLR                                        | TI               | ;get ready for next byte                        |                                  |

|                                                                                                          | RET                                        | `                |                                                 |                                  |

| In program                                                                                               | ming the                                   | e 8051 to recei  | ve character bytes serially                     |                                  |

| 1. TMOD reg                                                                                              | gister is                                  | loaded with the  | e value 20H, indicating the use of timer 1 in m | ode                              |

| (8-bit auto                                                                                              | -reload)                                   | to set baud rate | 2                                               |                                  |

| 2. TH1 is loa                                                                                            | ded to se                                  | et baud rate     |                                                 |                                  |

| 3. The SCON                                                                                              | V registe                                  | r is loaded with | the value 50H, indicating serial mode 1, whe    | re an 8-bit data is framed       |

| with start a                                                                                             | and stop                                   | bits             |                                                 |                                  |

| 4. TR1 is set                                                                                            | to 1 to s                                  | tart timer 1     |                                                 |                                  |

| 5. RI is cleared by CLR RI instruction                                                                   |                                            |                  |                                                 |                                  |

| 6. The RI flag bit is monitored with the use of instruction JNB RI, xx to see if an entire character has |                                            |                  |                                                 | entire character has             |

| been received yet                                                                                        |                                            |                  |                                                 |                                  |

| 7. When RI is raised, SBUF has the byte, its contents are moved into a safe place.                       |                                            |                  |                                                 |                                  |

| 8. To receive the next character, go to step 5.                                                          |                                            |                  |                                                 |                                  |

|                                                                                                          |                                            |                  |                                                 |                                  |

| Write a prog                                                                                             | ram for                                    | the 8051 to red  | ceive bytes of data serially and put them in P  | 1, set the baud rate at 4800, 8- |

| bit data and                                                                                             | 1 stop b                                   | it. (NOV 2016)   |                                                 |                                  |

| Solution:                                                                                                |                                            |                  |                                                 |                                  |

|                                                                                                          | MOV                                        | TMOD, #20H       | H ;timer 1, mode 2 (auto reload)                |                                  |

|                                                                                                          | MOV                                        | TH1, #-6         | ;4800 baud rate                                 |                                  |

|                                                                                                          | MOV SCON, #50H ;8-bit, 1 stop, REN enabled |                  |                                                 |                                  |

|                                                                                                          |                                            |                  |                                                 |                                  |

SETB TR1;start timer 1HERE:JNBRI, HERE;wait for char to come in

MOV A, SBUF ;saving incoming byte in A

MOV P1, A ;send to port 1

CLR RI ;get ready to receive next byte

SJMP HERE ;keep getting data

#### Unit-1

## In receiving bit via its RxD pin, 8051 goes through the following steps.

- 1. It receives the start bit

- Indicating that the next bit is the first bit of the character byte it is about to receive

- 2. The 8-bit character is received one bit at time

- 3. The stop bit is received

• When receiving the stop bit 8051 makes RI = 1, indicating that an entire character byte has been received.

- 5. After the SBUF contents are copied into a safe place.

- The RI flag bit must be forced to 0 by CLR RI in order to allow the next received character byte to be placed in SBUF.

- Failure to do this causes loss of the received character.

## There are two ways to increase the baud rate of data transfer

- To use a higher frequency crystal

- To change a bit in the PCON register

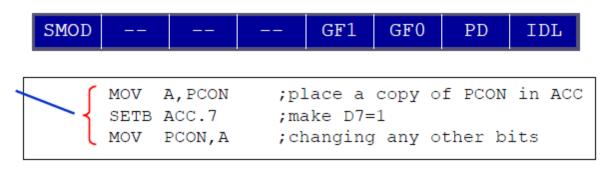

## PCON

- PCON register is an 8-bit register

- When 8051 is powered up, SMOD is zero.

- We can set it to high by software and thereby double the baud rate.

- GF1, GF0: General flag bits

- PD: Power down mode

- IDL: Ideal mode

Explain Pin details of 8051 microcontroller. (MAY 2006)

## Describe the functions of the following signals in 8051. RST, EA, PSEN and ALE. (NOV 2015)

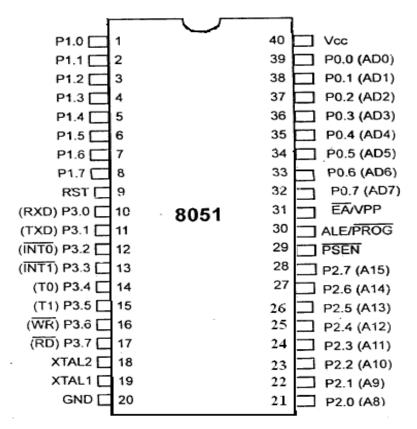

- ✓ The 8051 microcontroller is available as a 40 pin DIP chip and it works at +5 volts DC.

- ✓ Among the 40 pins, a total of 32 pins are allotted for the four parallel ports P0, P1, P2 and P3 i.e each port occupies 8-pins.

- ✓ The remaining pins are VCC, GND, XTAL1, XTAL2, RST, EA ,PSEN.

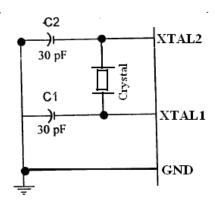

## XTAL1, XTAL2:

- ✓ These two pins are connected to Quartz crystal oscillator which runs the on-chip oscillator.

- ✓ The quartz crystal oscillator is connected to the two pins along with a capacitor of 30pF as shown in the circuit.